# RENESAS

# M62364FP/GP

# 8-bit 8ch Multiplying D/A Converter with Buffer Amplifiers

REJ03D0875-0400 Rev.4.00 Oct 02, 2009

### Description

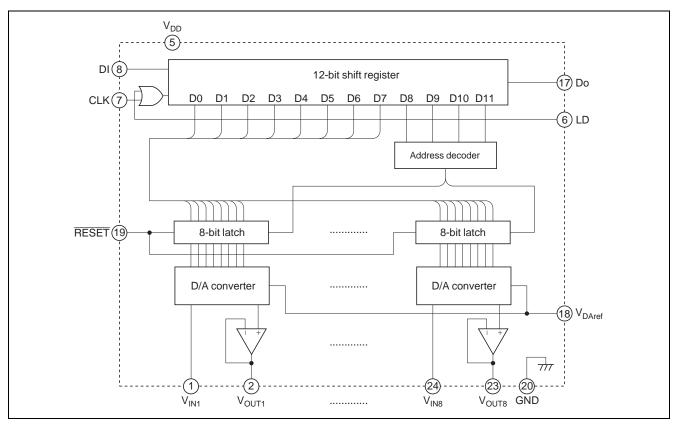

The M62364 is a CMOS 8-bit 8ch D/A converter having a multiplying function and output buffer amplifiers. It has a serial data input and can easily communicate with a microcontroller by the simple three-wiring method (DI, CLK, LD).

The output buffer amplifiers operating in AB-class has both sinking and driving capabilities of 1.0 mA or more and can operate in a whole supply range from  $V_{DD}$  to GND.

The IC is suitable for a use in automatic adjustment applications in conjunction with a MCU by utilizing the terminal  $D_0$  for a cascading connection.

### Features

- Three-wiring serial data transmission

- Doubled precision 8ch D/A converter employing an R-2R with higher-order segment method

- 8 buffer amplifiers operating in a whole supply voltage range from V<sub>DD</sub> to GND

- 4 quadrant multiplication

## Application

Digital to analog conversion for consumer and industrial equipment.

Gain setting and automatic adjustment of display-monitor and CTV.

### Block Diagram

RENESAS

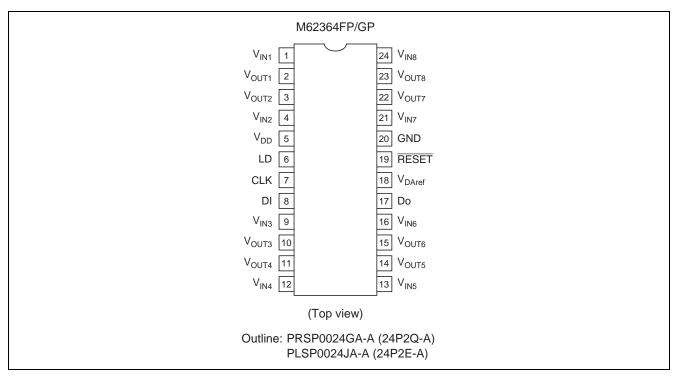

# **Pin Arrangement**

# **Pin Description**

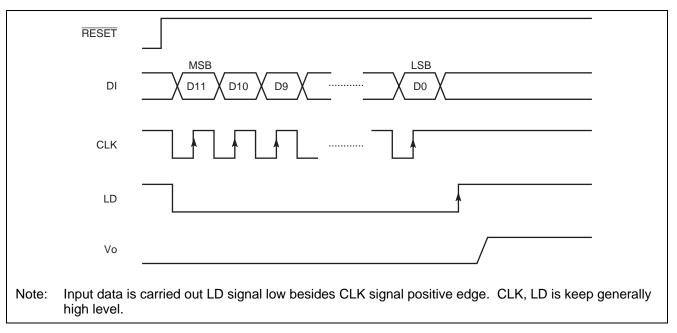

| Pin No. | Pin Name           | Function                                                                                                    |

|---------|--------------------|-------------------------------------------------------------------------------------------------------------|

| 8       | DI                 | Serial data input                                                                                           |

| 17      | Do                 | Serial data output                                                                                          |

| 7       | CLK                | Shift clock input. Input data of DI are taken into the 12-bit shift register on a rising edge of the clock. |

| 6       | LD                 | A low state enables data loading to the 12-bit shift register.                                              |

|         |                    | During a rising edge of LD, the data will be loaded to the output register.                                 |

| 19      | RESET              | Reset 8-bit latches                                                                                         |

| 2       | V <sub>OUT1</sub>  | D/A converter output with 8-bit resolution                                                                  |

| 3       | V <sub>OUT2</sub>  |                                                                                                             |

| 10      | V <sub>OUT3</sub>  |                                                                                                             |

| 11      | V <sub>OUT4</sub>  |                                                                                                             |

| 14      | V <sub>OUT5</sub>  |                                                                                                             |

| 15      | V <sub>OUT6</sub>  |                                                                                                             |

| 22      | V <sub>OUT7</sub>  |                                                                                                             |

| 23      | V <sub>OUT8</sub>  |                                                                                                             |

| 5       | V <sub>DD</sub>    | Power supply                                                                                                |

| 20      | GND                | Ground                                                                                                      |

| 1       | V <sub>IN1</sub>   | D/A converter input                                                                                         |

| 4       | V <sub>IN2</sub>   |                                                                                                             |

| 9       | V <sub>IN3</sub>   |                                                                                                             |

| 12      | V <sub>IN4</sub>   |                                                                                                             |

| 13      | V <sub>IN5</sub>   |                                                                                                             |

| 16      | V <sub>IN6</sub>   |                                                                                                             |

| 21      | V <sub>IN7</sub>   |                                                                                                             |

| 24      | V <sub>IN8</sub>   |                                                                                                             |

| 18      | V <sub>DAref</sub> | D/A converter reference voltage input                                                                       |

RENESAS

# **Absolute Maximum Ratings**

| ltem                  | Symbol             | Ratings                       | Unit |

|-----------------------|--------------------|-------------------------------|------|

| Supply voltage        | V <sub>DD</sub>    | –0.3 to +7.0                  | V    |

| Digital input voltage | V <sub>IND</sub>   | –0.3 to +7.0                  | V    |

| Analog input voltage  | V <sub>IN</sub>    | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Analog output voltage | V <sub>OUT</sub>   | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| D/A reference voltage | V <sub>DAref</sub> | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Operating temperature | Topr               | -20 to +75                    | °C   |

| Storage temperature   | Tstg               | -40 to +125                   | °C   |

# **Electrical Characteristics**

### <Ana/Dig Common Part>

$(V_{DD} = 5 \text{ V} \pm 10\%, V_{DD} \ge V_{IN}, \text{GND}, V_{DAref} = 0 \text{ V}, \text{ Ta} = -20 \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$

|                |                 |     | Limits |     |      |                                                   |

|----------------|-----------------|-----|--------|-----|------|---------------------------------------------------|

| Item           | Symbol          | Min | Тур    | Max | Unit | Conditions                                        |

| Supply voltage | V <sub>DD</sub> | 2.7 | 5.0    | 5.5 | V    |                                                   |

| Supply current | I <sub>DD</sub> |     |        | 3.5 | mA   | CLK = 1 MHz, $V_{CC}$ = 3 V, $I_{AO}$ = 0 $\mu A$ |

#### <Digital Part>

$(V_{DD} = 5 \text{ V} \pm 10\%, V_{DD} \ge V_{IN}, \text{GND}, V_{DAref} = 0 \text{ V}, \text{ Ta} = -20 \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$

|                                               |                  |                     | Limits |                     |      |                           |

|-----------------------------------------------|------------------|---------------------|--------|---------------------|------|---------------------------|

| Item                                          | Symbol           | Min                 | Тур    | Max                 | Unit | Conditions                |

| Input leak current                            | I <sub>ILK</sub> | -10                 |        | 10                  | μA   | $V_{IN} = 0$ to $V_{DD}$  |

| Digital input "Low" voltage                   | VIL              | —                   | _      | 0.2 V <sub>DD</sub> | V    |                           |

| Digital input "High" voltage                  | VIH              | 0.8 V <sub>DD</sub> | _      | _                   | V    |                           |

| D <sub>0</sub> terminal output "Low" voltage  | V <sub>OL</sub>  | —                   | _      | 0.4                 | V    | $I_{OL} = 2.5 \text{ mA}$ |

| D <sub>O</sub> terminal output "High" voltage | V <sub>OH</sub>  | $V_{DD} - 0.4$      |        |                     | V    | I <sub>OH</sub> = -400 μA |

#### <Analog Part>

| $(V_{} - 5 V + 10\%)$     | $V_{} > V_{}$ GND         | $V_{-1} = -0 V T_{2}$                                   | 20 to $\pm 85^{\circ}C$ unly | acc otherwise noted)  |

|---------------------------|---------------------------|---------------------------------------------------------|------------------------------|-----------------------|

| $(v_{DD} - J v \pm 10/0)$ | $v_{DD} \leq v_{IN}, OND$ | , $\mathbf{v}_{\text{DAref}} = 0 \mathbf{v}$ , $1a = 1$ | $2010$ $\pm 65$ C, unit      | ess otherwise noted.) |

|                                      |                    |       | Limits |                |      |                                                                                                       |  |

|--------------------------------------|--------------------|-------|--------|----------------|------|-------------------------------------------------------------------------------------------------------|--|

| Item                                 | Symbol             | Min   | Тур    | Max            | Unit | Conditions                                                                                            |  |

| Input current                        | I <sub>IN</sub>    |       | —      | 0.30           | mA   | $V_{IN} = 5 V, V_{DAref} = 0 V$                                                                       |  |

|                                      |                    |       |        |                |      | Proportional to Max. input current condition $(V_{IN} - V_{DAref})$ and digital data of each channels |  |

| D/A reference input                  | I <sub>DAref</sub> | -2.40 | —      | —              | mA   | $V_{IN} = 5 V, V_{DAref} = 0 V$                                                                       |  |

| current                              |                    |       |        |                |      | Proportional to Max. input                                                                            |  |

|                                      |                    |       |        |                |      | current condition $(V_{IN} - V_{DAref})$                                                              |  |

|                                      |                    |       |        |                |      | and digital data of each channels                                                                     |  |

| Resolution                           | RES                | _     | 8      | —              | bit  |                                                                                                       |  |

| Differential nonlinearity            | DNL                | -1    | _      | 1              | LSB  | V <sub>DAref</sub> = 0.050 V (10 mV/LSB)                                                              |  |

| Nonlinearity                         | NL                 | -1    | —      | 1              | LSB  | Without load ( $I_{AO} = \pm 0$ )                                                                     |  |

| Buffer amplifier output              | V <sub>AO</sub>    | 0.1   | _      | $V_{CC}-0.1$   | V    | $I_{AO} = \pm 100 \ \mu A$                                                                            |  |

| voltage range                        |                    | 0.2   | —      | $V_{CC} - 0.2$ |      | $I_{AO} = \pm 500 \ \mu A$                                                                            |  |

| Buffer amplifier output              | I <sub>AO</sub>    | -1    | —      | 1              | mA   | Upper saturation voltage = 0.4 V                                                                      |  |

| current range                        |                    |       |        |                |      | Lower saturation voltage = 0.4 V                                                                      |  |

| Output capacitive load               | Co                 | _     | _      | 0.1            | μF   |                                                                                                       |  |

| Buffer amplifier output<br>impedance | Ro                 |       | 5      |                | Ω    |                                                                                                       |  |

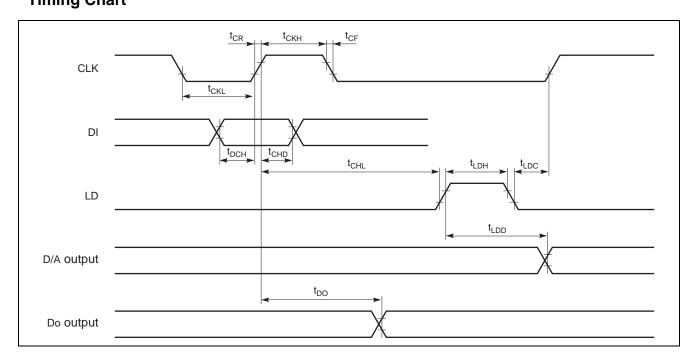

# **AC Characteristics**

| $(V_{DD} = 5 \text{ V} \pm 10\%, V_{DD} \ge V_{IN}, \text{GND}, V_{DAref} = 0 \text{ V}, \text{ Ta} = -20 \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$ |                  |     |        |     |      |                                                                             |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|--------|-----|------|-----------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                                                                              |                  |     | Limits |     |      |                                                                             |  |  |  |  |

| Item                                                                                                                                                                         | Symbol           | Min | Тур    | Max | Unit | Conditions                                                                  |  |  |  |  |

| Clock "L" pulse width                                                                                                                                                        | t <sub>CKL</sub> | 200 | —      | —   | ns   |                                                                             |  |  |  |  |

| Clock "H" pulse width                                                                                                                                                        | t <sub>скн</sub> | 200 | —      | —   | ns   |                                                                             |  |  |  |  |

| Clock rise time                                                                                                                                                              | t <sub>CR</sub>  | —   | —      | 200 | ns   |                                                                             |  |  |  |  |

| Clock fall time                                                                                                                                                              | t <sub>CF</sub>  | —   | —      | 200 | ns   |                                                                             |  |  |  |  |

| Data setup time                                                                                                                                                              | t <sub>DCH</sub> | 60  | —      | —   | ns   |                                                                             |  |  |  |  |

| Data hold time                                                                                                                                                               | t <sub>CHD</sub> | 100 | —      | —   | ns   |                                                                             |  |  |  |  |

| LD setup time                                                                                                                                                                | t <sub>CHL</sub> | 200 | —      | —   | ns   |                                                                             |  |  |  |  |

| LD hold time                                                                                                                                                                 | t <sub>LDC</sub> | 100 | —      | —   | ns   |                                                                             |  |  |  |  |

| LD "H" pulse duration time                                                                                                                                                   | t <sub>LDH</sub> | 100 | —      | —   | ns   |                                                                             |  |  |  |  |

| Data output delay time                                                                                                                                                       | t <sub>DO</sub>  | 70  | —      | 350 | ns   | C <sub>L</sub> = 100 pF                                                     |  |  |  |  |

| D/A output setting time                                                                                                                                                      | t <sub>LDD</sub> | _   | —      | 300 | μs   | $C_L \le 100 \text{ pF}, \text{ V}_{AO}: 0.1 \leftrightarrow 2.6 \text{ V}$ |  |  |  |  |

|                                                                                                                                                                              |                  |     |        |     |      | This time until the output becomes the final value of 1/2 LSB               |  |  |  |  |

# Timing Chart

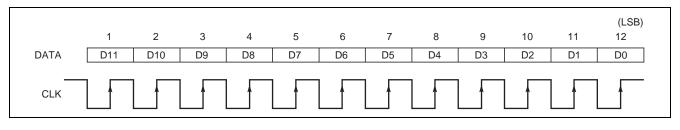

# **Digital Data Format**

#### 12-bit serial data

#### **Data Assignment**

| D0    | D1 | D2  | D3  | D4       | D5         | D6 | D7    | : DAC data |

|-------|----|-----|-----|----------|------------|----|-------|------------|

| (LSB) |    |     |     |          |            |    | (MSB) |            |

| D8    | D9 | D10 | D11 | : DAC se | elect data |    |       |            |

#### DAC Data

| D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D/A Output                                          |

|----|----|----|----|----|----|----|----|-----------------------------------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | V <sub>DAref</sub>                                  |

| 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | $(V_{IN} - V_{DAref}) / 256 \times 1 + V_{DAref}$   |

| 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | $(V_{IN} - V_{DAref}) / 256 \times 2 + V_{DAref}$   |

| 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | $(V_{IN} - V_{DAref}) / 256 \times 3 + V_{DAref}$   |

| :  | 1  | :  | :  | :  | :  | :  | :  | :                                                   |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | $(V_{IN} - V_{DAref}) / 256 \times 255 + V_{DAref}$ |

### DAC Select Data

| D8 | D9 | D10 | D11 | DAC Selection               |

|----|----|-----|-----|-----------------------------|

| 0  | 0  | 0   | 0   | Don't care                  |

| 0  | 0  | 0   | 1   | V <sub>OUT1</sub> selection |

| 0  | 0  | 1   | 0   | V <sub>OUT2</sub> selection |

| 0  | 0  | 1   | 1   | V <sub>OUT3</sub> selection |

| 0  | 1  | 0   | 0   | V <sub>OUT4</sub> selection |

| 0  | 1  | 0   | 1   | V <sub>OUT5</sub> selection |

| 0  | 1  | 1   | 0   | V <sub>OUT6</sub> selection |

| 0  | 1  | 1   | 1   | V <sub>OUT7</sub> selection |

| 1  | 0  | 0   | 0   | V <sub>OUT8</sub> selection |

| 1  | 0  | 0   | 1   | Don't care                  |

| 1  | 0  | 1   | 0   | Don't care                  |

| 1  | 0  | 1   | 1   | Don't care                  |

| 1  | 1  | 0   | 0   | Don't care                  |

| 1  | 1  | 0   | 1   | Don't care                  |

| 1  | 1  | 1   | 0   | Don't care                  |

| 1  | 1  | 1   | 1   | Don't care                  |

# Timing Chart (Model)

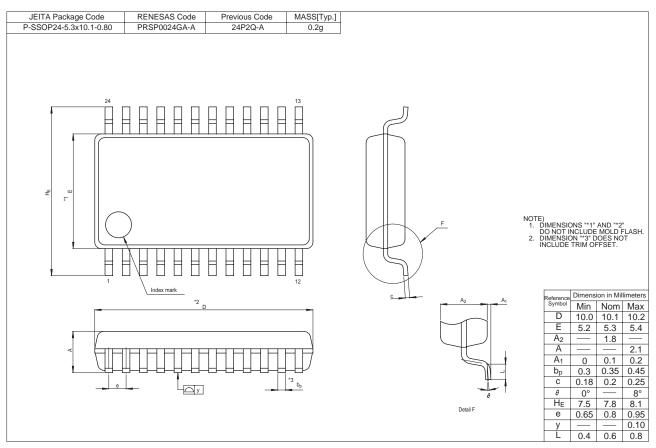

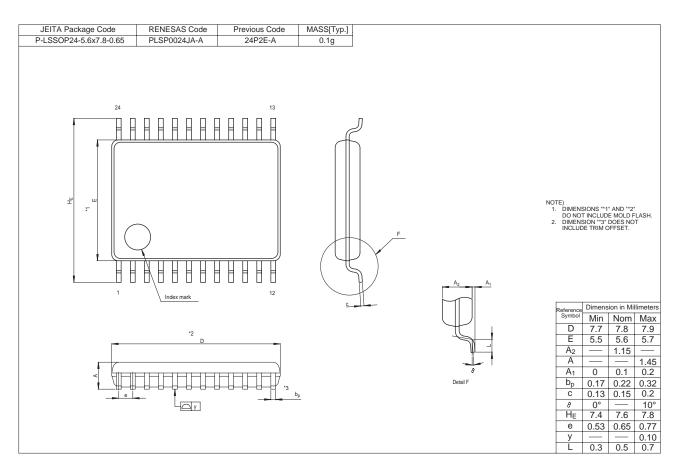

## **Package Dimensions**

RENESAS

# **Ordering Information**

| Part No.                                | Package Name | Package Code | Taping Spec. |

|-----------------------------------------|--------------|--------------|--------------|

| M62364FP#DF1J,DF1G,DF2G, TF1J,TF1G,TF2G | 24P2Q-A      | PRSP0024GA-A | 2,000/Reel   |

| M62364GP#DF, TF                         | 24P2E-A      | PLSP0024JA-A | 2,500/Reel   |

### RenesasTechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

#### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

### Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com